| |

|

Меню

Главная

Прикосновение космоса

Человек в космосе

Познаем вселенную

Космонавт

Из авиации в ракеты

Луноход

Первые полеты в космос

Баллистические ракеты

Тепло в космосе

Аэродром

Полёт человека

Ракеты

Кандидаты наса

Космическое будущее

Разработка двигателей

Сатурн-аполлон

Год вне земли

Старт

Подготовки космонавтов

Первые полеты в космос

Психология

Оборудование

Модель ракеты

|

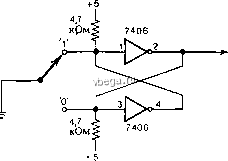

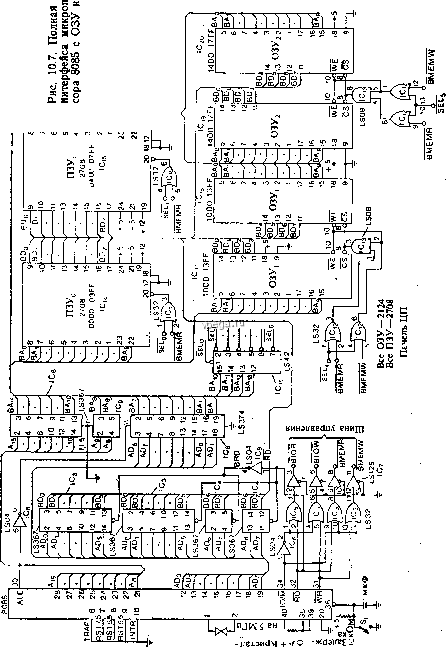

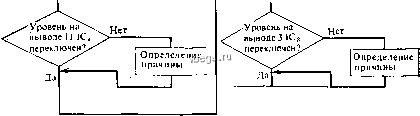

Космонавтика Архитектура 3-х шинных систем системные данные, при операции ЗАПИСЬ - данные, выводимые УТСС. Это возможно, поскольку выходные формирователи 1Сз и IC4 блокируются на время операции ЧТЕНИЕ. Рассмотрим, каким образом осуществляется блокировка этих формирователей при выполнении операции ЧТЕНИЕ. На рис. 10.5 показана секция устройства УТСС, используемая для регулирования логических уровней сигналов некоторых управ-ляющих выводов микропроцессора 8085. Эти выводы обозначены как RiD, WR, IO/M, ALE. Существуют другие управляющие Выход  Рис. 10.6. Построение схемы гашения выброса с помощью двух инверторов со свободным коллектором типа 7406. ВЫВОДЫ микропроцессора 8085, такие, как So и Si; однако они не используются в нащей системе. Если же в проектируемой системе используются другие управляющие выводы, то для регулирования логических уровней состояний УТСС следует применить подобные же средства. Рассмотрение событий, происходящих в течение выполнения операци ЧТЕНИЕ микропроцессора 8085, показывает, что одним из основных событий является выдача сигнала RD. При переходе этого сигнала в состояние, соответствующее логическому О, микропроцессор выполняет операцию чтения либо из памяти, либо с устройства ввода, что идентифицируется логическим состоянием сигнала IO/M. По этой информации УТСС определяет необходимость блокировки выходных формирователей 1Сз и IC4. Устройство 74LS367 блокируется, если на выводы 1 и 15 поступает сигнал уровня логической 1. Следовательно, в случае когда сигнал соответствует логическому О, на эти выводы устройства 74LS367 необходимо подать сигнал 1. Это достигается путем подачи на блокирующие выводы 1 и 15 схем IC3 и IC4, приведенных на рис. 10.2, сигнала RD, как это показано на рнс. 10.5. Соответстаующее соединение осуществляется всякий раз, когда сигнал RD есть О, что определяет операцию ЧТЕНИЕ для УТСС микропроцессора 8085. При этом светоизлучающие диоды отображают данные, вводимые в микропроцессор. Управляющие сигналы УТСС поступают на фиксатор, как это показано на рис. 10.6, используемый с целью предотвращения выброса сигнала, обусловленного действием механического переключателя. Может возникнуть вопрос, почему бы не поставить подобные схемы для каждого переключателя? Это не делается по той причине, что адресные линии и линии данных микропроцессора не оказывают влияния на коммуникационные взаимодействия в системе до тех пор, пока эти взаимодействия не распознаны посредством управляющих сигналов. Именно с помощью управляющих сигналов и осуществляется стробирование данных, передаваемых во внешние схемы. Для каждого положения переключателя требуется один стробирую-щий сигнал. Схемы, предотвращающие выброс, можно, по желанию, установить для каждого переключателя, однако это не является необходимым. 10.3. Замечания по отладке технических средств системы Рассмотрев особенности схемной реализации УТСС, изложим в общих чертах один подход, используемый для эффективной отладки технических средств системы. Существо подхода заключается в определении правильности функционирования всех коммуникационных каналов в системе. При этом не принимаются во внимание вопросы синхронизации сигналов, а определяется возможность электрического взаимодействия микропроцессора со всеми логическими устройствами в системе. Подобная проверка имеет большое значение для отладки технических средств системы. Тестирование посредством статических сигналов предоставляет средства для осуществления проверки всех коммуникационных каналов системы. Это является большим достоинством данного метода, поскольку отпадает необходимость в проектировании специальных схем тестирования в рамках специфических тестирующих устройств микропроцессорной системы. Кроме того, основные средства устройства тестирования могут быть реализованы технически при минимальных затратах. Это дает возможность каждому пользователю, занимающемуся проектированием системы на базе микропроцессора либо поиском в ней неисправностей, иметь мощные средства отладки системы. При использовании УТСС последнее подсоединяется к системе посредством кабеля, как показано в гл. 5. Последовательно рассмотрим проверку всех технических средств системы. При этом УТСС используем как средство отладки системы на Глава 10 базе микропроцессора 8085. Однако приводимого материала достаточно для построения УТСС для проверки системы на базе любого другого микропроцессора. 10.4. Отладка адресной шины системы Полная схема интерфейса микропроцессора 8085 с ПЗУ и ОЗУ приведена на рис. 10.7. В последующем мы будем достаточно часто обращаться к рис. 10.7. Поэтому желательно каким-либо образом пометить этот рисунок, например с помощью бумажной полоски. Это позволит быстро его отыскивать каждый раз, когда в этом будет возникать необходимость. Адресная шина системы-это первый компонент системы программирования ППЗУ, для которой мы будем осуществлять проверку прохождения электрических сигналов. Определим, возможна ли передача сигналов логических о и 1 по адресным линиям ВАо-BAi5. С этой целью введем представленный на рис. 10.1 УТСС в проверяемую систему вместо микропроцессора путем установки вилки УТСС в гнездо подключения микропроцессора. Проще всего проверить адресные линии ВАз- BAi5, поскольку последние в отличие от адресных линий ВАо- ВА? не имеют временного мультиплексирования . Процедура проверки линий BAs-BA15 посредством УТСС 1. Установить переключатели УТСС, помеченные как SAs- SA16, в положение, соответствующее логическому о на выходе. 2. Соединить с землей один конец пробника логического уровня DVM (или VOM). 3. Соединить другой конец пробника напряжения с выводом 5 IC9 системы (рис. 10.7). 4. Напряжение должно соответствовать логическому уровню 0. 5. Переключить SAs УТСС в положение, соответствующее логической 1. 6. Напряжение на выводе 5 IC9 (рис. 10.7) должно соответствовать уровню логической 1. 7. Теперь обеспечено переключение адресной линии ВАз с уровня логического о на уровень логинеской 1. 8. Повторить шаги 3-7 для каждой адресной линии BAg- BA16, проверяя наличие требуемых уровней напряжения на соответствующих выводах устройства. 9. В случае отсутствия переключения сигнала на адресной линии статически исследуется причина наполадки. 10. Теперь проверено, что для всех адресных линий ВАз- BA16 производится переключение сигнала с уровня о на уро- te Г) sj  ИИЯЭФНИ1Г s oaoioj Начало SAj-SA,5 = логический О на УТСС Переключение SA, на УТСС ....Уровень на выводе 5 1С, дереключен? Уровень на выводеЗ ICg переключен ?

Определение причины

Определение причины

Определение причины  Переключение 5А на УТСС  Переключение SAijHa УТСС Уровень на выводе 5 ICj переключен? Определение причины ---- Определение причины -1-~ . Нет

Определение причины Проверка B.-g-BA завершена успешно Рис. 10.8. Блок-схема алгоритма проверки выходов BAj-ВА15 адресной шины микропр-оцессора 8085. вень 1 под управлением микропроцессора; либо обнаружено, что для некоторых линий такое переключение отсутствует, что требует дальнейшего исследования (с этой целью осуществляется проверка каждой цепи схемы путем прослеживания уров ня напряжения в выбранных точках на протяжении . всего информационного канала). На рис. 10.8 приведена блок-схема последовательности действий при проверке адресных линий ВАа-BA15. Вспомним, что мы не определяли правильность подсоединения линий ВАа- BAi5 в системе. Этот вопрос будет затронут в данной главе позднее. Определим теперь возможность переключения линий ВАо- ВА7 с уровня логической 1 на уровень логического 0. Соответствующая процедура несколько сложнее процедуры для адресных линий ВАа-ВА15. Процедура для проверки адресных линий ВАо-ВА7 1. Установить переключатели, помеченные So-S7, в поло-жение, соответствующее логическому 0. 2. Установить управляющие переключатели УТСС следующим обр азом : а) WR=логическая 1 (нерабочее состояние); б) RD=логическаяЛ (нерабочее состояние); в) 10/М=логическая 1 (безразлично); г) ALE=логический О (нерабочее состояние). 3. При сигнале.RD, соответствующем логическому О, светоизлучающие диоды будут (должны) отображать информацию, установленную с помощью переключателей So-S7. 4. Установить RD в положение, соответствущее логической 1. При этом светоизлучающий диод Do должен начать светиться. 5. Перебросить управляющий переключатель ALE из состояния О в состояние 1. 6. Установить управляющий переключатель ALE обратно в состояние 0. Последовательность шагов 5 и б приводит к фиксации адресных разрядов. 7. Измерить напряжение на выводе 10 1С. Это напряжение должно соответствовать значению уровня логической 1. 8. Установить So в положение, соответствующее логической 1. 9. Повторить шаги 4-8 для каждой адресной линии ВАо- ВА7. Если на шаге 7 выходной сигнал не соответствует введенным данным, повторить процедуру с шага 3 и измерить напряжения на каждом шаге с целью проверки логической корректности сигналов. Нашей целью является реализация общей функции фикса-

|

|||||||||||||||||||||||||||||||||